Az új gyártástechnológiák bevezetése sok szempontból nehézkes, egyrészt magának a node-nak megfelelően kell működnie, másrészt a kihozatalnak fokozatos javulást kell mutatnia, elvégre a tapasztalatokra alapozó módosításokkal csökkenthető a hibasűrűség, vagyis az egységnyi területre levetített hibák száma, amelyek potenciálisan rossz lapkákat eredményezhetnek egy waferen.

David Schor nemrég beszámolt róla, hogy a VLSI 2019-es rendezvényen a TSMC nyilvánosságra hozta az első generációs 7 nm-es gyártástechnológiájukra vonatkozó eredményeket, amely szerint történetük legjobb csökkentését produkálták a hibasűrűség (D0) tekintetében. A nagyobb lapkák tekintetében az N7-es node már egy szinten van 16FF node-dal, az N10-hez képest pedig jobbnak tekinthető.

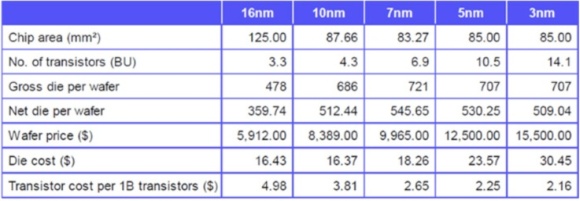

(forrás: IBS Research)

Ez a partnereknek mindenképpen jó hír, de nagyon olcsó gyárthatóságot még nem jelent, ugyanis a Bits And Chips megemlítette, hogy az IBS Research elemzése szerint a waferár eléggé magas, majdnem a 16 nm-es node kétszerese. Ez egyébként a jövőben is emelkedni fog, hiszen az új generációs gyártástechnológiák kidolgozása drágul, tehát ebből a szempontból sok jóra nem számíthat a piac.